從原子到電路 納米集成電路制造中的金屬薄膜沉積工藝與設計協同

在當今信息時代,集成電路(IC)是數字世界的基石,而其性能的持續飛躍,直接依賴于制造工藝的不斷精進。當工藝節點進入納米尺度,集成電路的制造已堪稱人類工程學的巔峰。其中,金屬薄膜沉積與金屬化工藝,作為連接數以億計晶體管、構建電路互聯網絡的核心步驟,與集成電路設計理念深度耦合,共同決定了芯片的速度、功耗、可靠性與集成度。本文將探討納米尺度下金屬薄膜沉積的關鍵工藝,并闡釋其與集成電路設計的緊密互動。

一、納米集成電路制造工藝概覽

納米集成電路制造是一個極其復雜且精密的系統工程,通常涉及數百道工序。其核心流程可概括為:在硅襯底上通過光刻、刻蝕、離子注入、薄膜沉積等工藝,循環往復地構建出晶體管的三維結構(前端工藝,FEOL),隨后通過多層金屬互連將這些晶體管連接成功能電路(后端工藝,BEOL)。隨著工藝節點從28nm、14nm向7nm、5nm乃至更小尺寸演進,線寬不斷縮小,互連層的堆疊數量不斷增加(可達十余層),這對金屬化工藝提出了前所未有的挑戰:如何在高深寬比的狹窄溝槽中填充導電性能優異、無缺陷的金屬導線,并控制其電阻、電容及電遷移效應。

二、金屬薄膜沉積工藝及金屬化:納米尺度的關鍵挑戰

金屬化是指在集成電路的介電層(如二氧化硅)中刻蝕出圖形化的溝槽和通孔,并填充金屬以形成互連導線和接觸孔/通孔的過程。金屬薄膜沉積是其中的核心工藝,主要有以下關鍵技術:

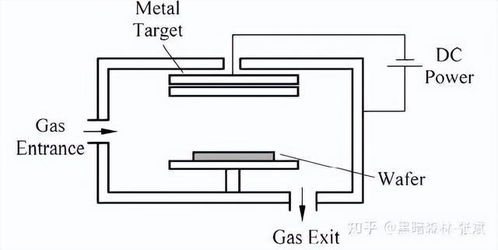

- 物理氣相沉積(PVD):傳統且關鍵的工藝,主要用于沉積金屬擴散阻擋層(如TiN/TaN)和粘附層(如Ti)。在PVD中,高純度的金屬靶材在真空腔體內被高能粒子轟擊,濺射出金屬原子,這些原子沉積在硅片表面形成薄膜。在納米節點,PVD技術面臨臺階覆蓋率和填充高深寬比結構能力不足的挑戰,因此常與其他技術結合使用。

- 化學氣相沉積(CVD)與原子層沉積(ALD):這兩種氣相沉積技術能提供極佳的臺階覆蓋率和均勻性。CVD通過氣態前驅體在襯底表面發生化學反應形成固態薄膜。而ALD是CVD的更高級形式,通過將前驅體氣體交替脈沖通入反應腔,每次脈沖僅在表面形成單原子層,從而實現原子級精度的厚度控制和完美的共形覆蓋。在納米工藝中,ALD被廣泛用于沉積超薄(幾個納米厚)且均勻的擴散阻擋層和襯墊層,這對防止銅原子向介電層擴散至關重要。

- 電化學沉積(ECD)——銅互連的基石:自130nm節點以來,銅因其更低的電阻率和更強的抗電遷移能力取代鋁成為主流互連材料。銅的大馬士革工藝是金屬化的核心:先沉積阻擋層和銅種子層(通常由PVD完成),然后通過ECD將銅離子從電解液中電鍍到種子層上,完全填充溝槽和通孔。ECD工藝必須實現無孔洞、無縫隙的“超填充”,這對電解液成分、添加劑控制和工藝參數提出了極高要求。填充后,需要通過化學機械拋光(CMP)去除表面多余的銅,使金屬導線平坦化。

三、金屬化工藝與集成電路設計的協同優化

集成電路設計并非在制造工藝完成后才進行,而是必須與制造工藝協同設計(Design for Manufacturing, DFM)。金屬化工藝的物理限制直接影響設計規則和電路性能:

- 設計規則制定:工藝工程師根據PVD、ALD、ECD和CMP等工藝的實際能力(如最小線寬、間距、通孔覆蓋度等),為設計人員制定嚴格的設計規則。例如,規定金屬線的最小寬度和間距以防止短路或斷路,規定通孔與金屬線的重疊余量以確保可靠連接。在納米尺度,這些規則異常復雜,必須通過電子設計自動化(EDA)工具嚴格檢查。

- 互連寄生參數提取與建模:金屬導線的電阻(R)和線與線之間的電容(C)構成了互連寄生RC延遲。在納米節點,互連延遲已超過晶體管門延遲,成為制約芯片速度的主要瓶頸。設計工具必須基于實際的金屬薄膜厚度、線寬、介電材料常數等工藝參數,精確提取和建模互連網絡的RC參數,以便在設計階段進行時序分析和優化。

- 可靠性驅動的設計:電遷移是金屬導線在高電流密度下原子定向遷移導致的失效現象。設計時需要根據工藝提供的金屬電流承載能力,規劃足夠的線寬,并對時鐘網絡、電源網格等關鍵網絡進行特殊優化。熱效應也與金屬互連密切相關,設計需考慮互連產生的焦耳熱及其散熱路徑。

- 新結構與新材料探索:為應對RC延遲挑戰,設計和工藝共同推動創新。例如,采用低k介質材料降低電容;探索空氣隙(Air Gap)隔離技術;研究鈷、釕等新型阻擋層和襯墊材料以減小有效導線電阻;甚至研究碳納米管、石墨烯等革命性互連方案。這些新工藝的實現,都需要設計端提供相應的測試結構和評估電路。

結論

納米集成電路的制造是一個集物理學、化學、材料科學與電子工程于一體的尖端領域。金屬薄膜沉積與金屬化工藝,作為構建芯片“神經網絡”的微血管手術,其精度與可靠性直接決定了芯片的最終性能。而現代集成電路設計已深度融入工藝的物理現實,兩者在“設計-工藝協同優化”(DTCO)的框架下緊密互動、迭代前行。從原子層沉積的精確控制,到銅互連的無缺陷填充,再到設計規則中的每一條約束,無不體現著人類在納米尺度上駕馭物質、構建智能的非凡努力。隨著摩爾定律的持續推進,金屬化工藝與集成電路設計的協同創新必將邁向更加精細和智能的新階段。

如若轉載,請注明出處:http://www.mikuyyi.cn/product/73.html

更新時間:2026-04-12 01:15:51